通往AI化EDA之路的研究综述

发布时间:2022-12-12 07:00

摘 要

机器学习方法在图像、语音及文本等领域的突破性进展吸引着EDA领域众多的研究者。近几年来,越来越多的EDA研究工作中引入了机器学习的方法,在指标预测(Prediction)、过程优化(Optimization)、提前诊断(Detection)等方面起到了极大的促进作用。研究的方法包括同类问题的转换,比如版图问题转为图像问题,综合和布局问题转为图问题;引入了强化学习及对抗网络,也很好地解决EDA中的相关问题。

从ML-assisted EDA到ML-base EDA

芯片设计是一笔关于人力,工具和时间的经济账,同时追求的是更好,更快和更便宜的设计目标,而现实的矛盾在于三者只取其二[1]。从摩尔定律来看,芯片的集成能力(scaling)需要保持每周1%的提升;而后摩尔时代,面临更高工艺和更复杂设计的考验。在芯片设计领域起着桥梁作用的EDA(Electronic Design Automation)工具发挥着至关重要的作用,EDA衔接设计和加工,贯穿于芯片制造的全流程之中。面临着芯片设计领域的新挑战,已有50年发展历史的EDA也正在寻求新的突破。

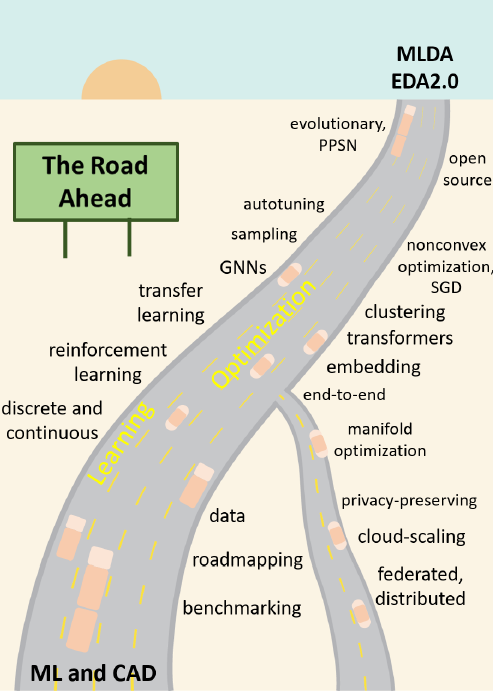

近10年来,随着机器学习技术在图像、语音及文本处理等方面的突破性进展,机器学习的方法也越来越多地被引入到EDA领域,现有的众多研究让EDA重新焕发活力。在论文中[2]提出了从ML-assisted EDA走向ML-based EDA之路,在通向智能化的EDA之路上需要结实可靠的路基作为保证,机器学习的相关方法正发挥着这样的作用,加速芯片设计的全流程,最终助力芯片设计实现“自动驾驶”(全自动化)。

图1 通向ML-based EDA之路[2]

图片来源:https://ieeexplore.ieee.org/document/9829233

研究总结

目前ML在EDA领域的研究或者技术应用,仍处于AI-assisted 阶段,通过AI赋能芯片设计,达到“将本增效”的目的,将工程师从繁琐重复性的工作中解放,投入到更加核心的工作。

纵观近些年来的ML在EDA领域的研究,大概可以总结为以下几个方面:

1. ML在EDA研究中的工作主要聚焦在指标预测(Prediction)、过程优化(Optimization)、提前诊断(Detection)方面,在这三方面已经取得了不错的成果,对于提升芯片设计质量和加快芯片设计流程具有很大的帮助。比如采用CNN的方法在布局阶段对布线的可行性和DRV(Design Rule Violation)进行预测;在掩膜综合(Mask Synthesis)阶段采用CGAN(Conditional Generative Adversarial Network)模型优化边缘放置误差;利用CNN网络对光刻中热点(hotspot)进行提前的诊断。

2. 研究方法涵盖采用ML助力传统算法、类比问题的迁移和无监督学习。助力传统算法的研究中,由于EDA中的问题是多组合问题,仅靠ML算法无法解决,但可以将ML算法来加速传统算法的计算,比如在逻辑综合中处理拥塞问题;类比问题的研究方法中,将EDA中的问题转换为图像问题或者图问题,并结合迁移学习的方法,比如布局后的版图(网表转换成代表电路的几何图形)可以转换为图像问题,使用CNN处理;逻辑综合(Logic Synthesis)和布局规划(Placement)等网表具有图特征,可以将此类问题转换为图问题,使用Graph-NN处理;无监督学习的典型是采用对抗网络(GAN:Generative Adversarial Network)的方式生成数据,减少对数据集的依赖。

3. 传统的ML方法使用度在逐渐下降,比如Q-learning,基于神经网络的ML方法广泛应用到EDA领域中,比如CNN模型,cGAN(Conditional Generative Adversarial Network),强化学习和图网络(Graph Neural Network)。

4. 研究工作中开始注重泛化能力,不仅解决研究中针对的benchmark,同时注重通用性,扩大使用范围。

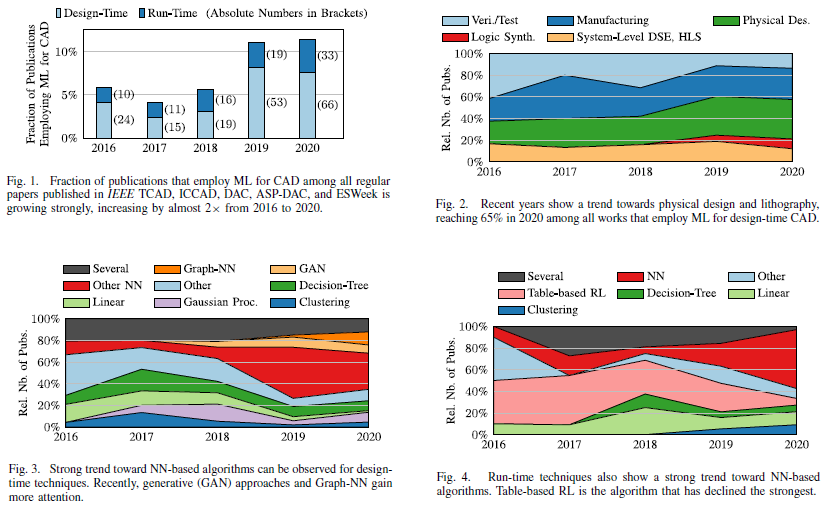

图2 2016年到2020年发表在EDA会中使用ML方法的文章分析[3]

图片来源:https://ieeexplore.ieee.org/document/9598835

如图2 所示,论文[3]中统计了从2016年到2020年正式发表在EDA领域顶会IEEE TCAD, ICCAD, DAC, ASP-DAC和ESWeek的文章,1)将ML方法应用到EDA研究的论文数量已经翻倍;2)ML在EDA中的物理设计和芯片制造研究应用中越来越多;3)在众多ML方法中,Graph-NN和GAN的模型得到越来越多的应用;4)Run-time(硅后)阶段 也开始大量使用NN(Neural Network)的方法。文章中对EDA的设计环节、对应的问题以及常用的ML方法总结如下图。

图3 EDA中相关的设计环节、对应的问题以及常用的ML方法总结[3]

图片来源:https://ieeexplore.ieee.org/document/9598835

相关研究介绍

芯片设计是一个性能驱动的过程,设计的过程中不断追求最佳的特性指标。芯片特性可以分为设计时特性(Design-time)和运行时(Run-time)特性,也可以称之为硅前(Pre-silicon)特性和硅后(After-silicon)特性。设计时特性包括布线拥塞(Routing Congestion)、DRC规则检查(Design Rule Checking Violation)以及最终设计的特性,如功耗、性能和面积。运行阶段的特性包括平台特性,如功耗;和使用场景中所使用的模型的特性,比如workload运行的性能。

特性预测使用的算法多为监督学习方法,训练以输入和输出数据集为依据进行迭代。此类方法重点解决的是回归问题或者是分类问题。当然,也可以在传统方法中调用深度学习的推理过程,但由于传统方法的局限和复杂性,限制了所使用模型的复杂度。从论文中也可以看出所使用的CNN网络结构相对简单,多以全连接为主。

特性预测还可以反输入到设计中约束设计的空间探索(Design Space Exploration)得到更加优化的结果,这也是现在研究中的一个方向,优化现有方法的结果。

另外,随着GPU算力的提升,在EDA的布局过程中也开始尝试引入GPU的并行能力加速计算过程。

1. 高层次综合的拥塞、资源分配和时序(Timing)问题

高层次综合(HLS:High Level Synthesis)是将高层次的语言比如C/C++/System-C 的硬件描述语言自动化地转换为Verilog或者VHDL,采用高级语言开发可以大幅提升开发效率,尤其是在FPGA领域,比如Xilinx基于HLS开发了一系列的图像处理库。衡量HLS综合的指标包括拥塞处理、使用的逻辑资源和时序(最大工作频率)等。

针对HLS综合中的问题可以采用近似模型(Surrogate Model)的方式加速问题的解决,用ML的方法在有监督的情况下学习综合的过程,然后将所学的模型应用到综合过程中。

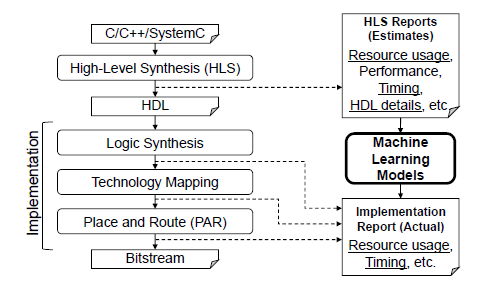

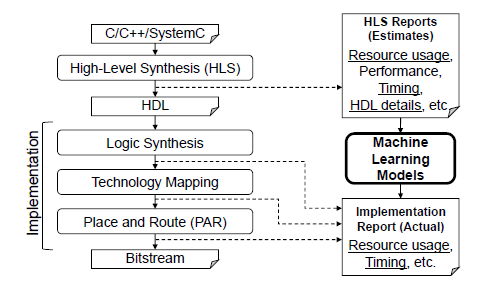

论文[4]采了类似的方法,用类MLP的网络训练HLS综合的输出报告,再用训练的model分析不同阶段的资源使用率,比如RAM,LUT及DSP等。

图4 论文[4]中使用ML方法的HLS综合流程

图片来源:https://ieeexplore.ieee.org/document/8457644

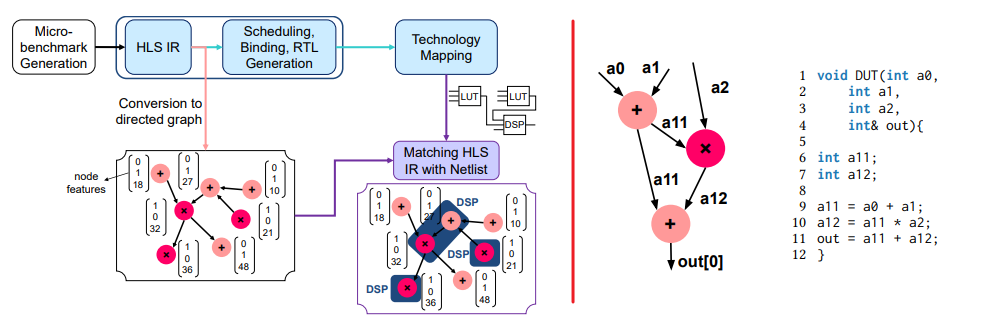

论文[5]中提出了基于Graph-NN预测FPGA内部电路延时的方法,在延迟预测中运算操作到FPGA的硬核(如DSP)的映射决定了延迟,这种映射依赖数据流图的局部结构,论文中使用Graph-NN网络(GraphSAGE和D-SAGE)用来捕捉节点的局部结构来预测延迟。如下图所示,左图为基于Graph-NN的处理流程,将HLS的IR转换为有向图,然后映射到网表;右图表示HLS语言转换为有向图。

图5 论文[5]中使用Graph-NN预测电路延迟的流程图

图片来源:https://www.csl.cornell.edu/~zhiruz/pdfs/dsp-gnn-iccad2020.pdf

论文[6]则是在进行HLS综合之前,在LLVM IR层级对并行度、pragma参数(如tile size, unrolling和pipelining)和FPGA资源在动态trace性能的监督下进行快速的空间探索,而后使用空间探索的结果指导HLS的综合。

图6 论文[6]中针对HLS中多层级并行度进行空间探索的框架

图片来源:https://ieeexplore.ieee.org/document/7927161

2. 逻辑综合中的功耗和面积问题

逻辑综合是将RTL代码转换为特定工艺下的门级电路的网表,网表是一个元器件互联的图,因此特别适合采用Graph-NN的方法进行处理。典型研究如论文[7],文中采用Graph-NN统计在组合电路上传播信号的平均反转率评估功耗,由于是在门级电路的细颗粒度,这种方法对于不同的负载和电路有具有很好的泛化作用。论文[8]使用NN的方法预估近似电路的误码率(error rate of an approximate circuit),针对特定电路,通过删除或者添加门级电路逼近实际的电路,以输出的误码率作为评价标准。同时根据预测的误码率不断迭代,实现功耗和面积的最小化。

3. 布局中规则检查预测

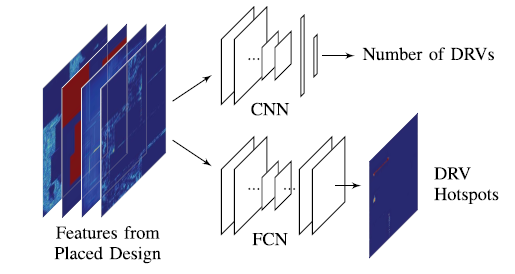

布局算法虽然发展了几十年,但是随着工艺越来越先进,门级电路越来越庞大,合理的布局仍然是一项巨大的挑战。论文[9]提出了两种类图像领域中的CNN网络来预测DRV,CNN网络用预测DRV的数量,全CNN网络用来预测DRV热点(hotspot)的位置,如下图所示。

图7 论文[9]中使用CNN进行DRV检查的示意图

图片来源:https://ieeexplore.ieee.org/document/8587655

4.布线中的拥塞问题

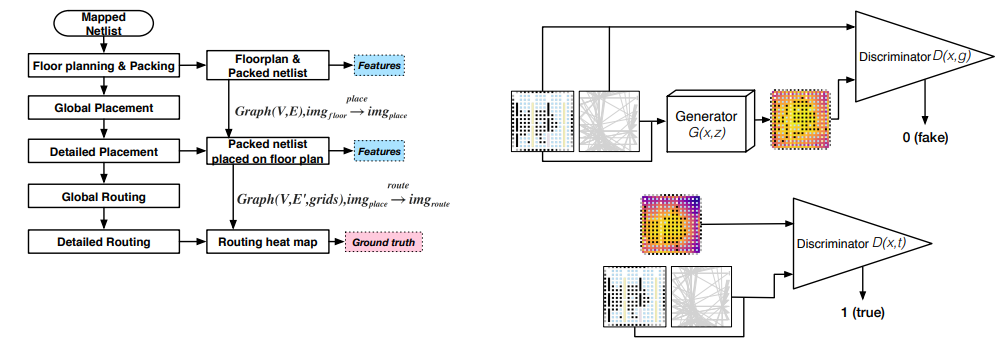

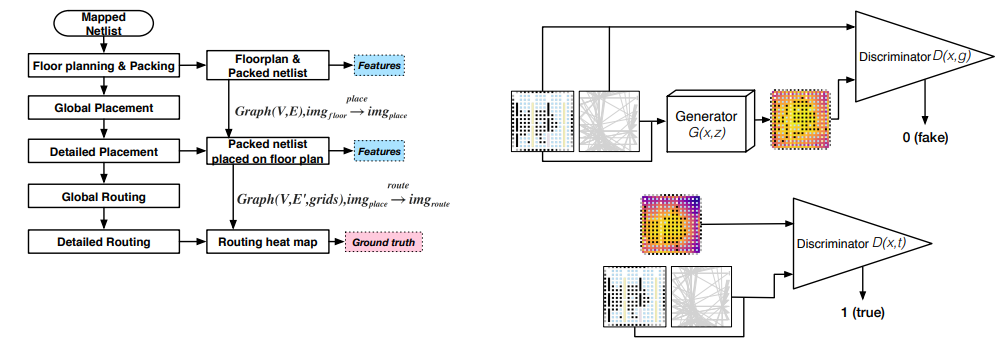

布线过程属于多组合问题,寻求最优解的过程十分复杂,如果仅仅依靠ML是不可行的,因此现有的研究中采用ML和传统结合的方法。在实践中也发现,在布线的优化方法中,往往是多种方法均可以达到相同的效果,因此像输出和输入相对应的监督学习方法变得不实用,反而是诸如GAN这种生成模型得到广泛的应用。

论文[10]使用CGAN方法在布局阶段预测布线中的拥塞,将拥塞的预估转换为图像的热力图分析问题。训练数据仅需要布局阶段的特征,而不需要布线阶段的特征,通过CGAN中的生成器生成的fake数据和真实数据混叠一起,使用鉴别器进行鉴别训练。

图8 论文[10]中使用CGAN进行物理设计的流程图和CGAN中的生成器和鉴别器

图片来源:https://arxiv.org/abs/1904.07077

5.掩膜精度的预估

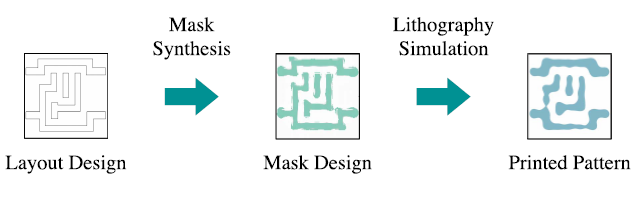

光刻决定了印制的精度和加工过程中的鲁棒性。典型掩膜综合和验证流程如下图所示:Layout后的版图经过掩膜综合生成掩膜设计,再经过光刻仿真生成印制版图。

图9 掩膜综合和验证的典型流程[3]

图片来源:https://ieeexplore.ieee.org/document/9598835

掩膜综合的过程主要包括两个优化:亚分辨率辅助功能(SRAFs: Sub-Resolution Assistant Features)和光学邻近校正(OPC: Optical Proximity Corrections)。衡量掩膜综合指标为边缘放置误差(EPE: Edge Displacement Errors)和工艺偏差环(PVBands: Process Variation Bands)。

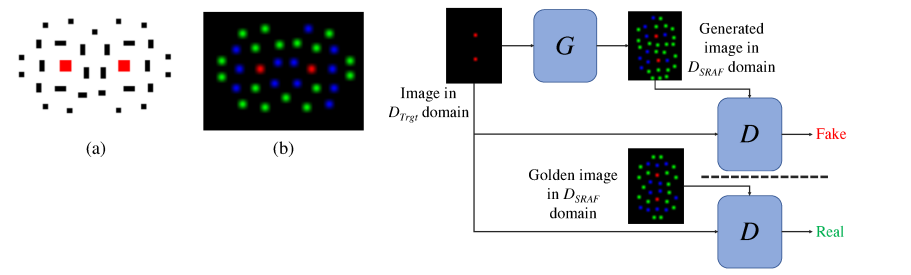

论文[11]使用多通道热力图编码方法来处理SRAF的不同的尺寸规则,如下图的作图所示,经过编码后转为图像问题,然后利用cGAN网络预测SRAF优化的的结果。

图10 左图为多通道热力图编码,a为原始layout图,b为编码后的layout图;右图为cGAN网络的框图[11]

图片来源:https://ieeexplore.ieee.org/document/9094711

6. 逻辑综合中的优化

论文[12] 提出了使用强化学习的方法在时序约束的条件下优化与非门图,该方法使用7维向量表示网络状态,如下图中的右图所示。在强化学习中使用Advantage Actor Critic agent (A2C),每一步从7种action种选择一种。这种随机状态的设计方法使得训练的模型具备很好的泛化能力。

图11 论文[12]中的强化学习流程图和所选择的7种状态

图片来源:https://arxiv.org/abs/1911.04021

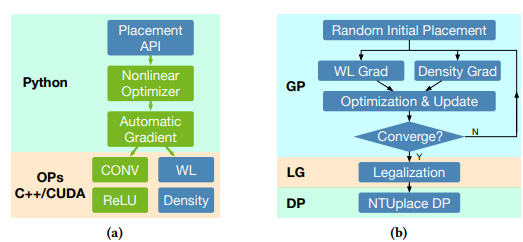

7.使用GPU的并行化加速布局

基于GPU的并行化(多线程)的加速技术也逐渐用到EDA工具中。在论文[13]中,作者将全局的布线优化转换为NN训练问题,训练过程中通过定制化kernel的方式发挥GPU的并行能力,先相比于此前的多线程布局算法获得30倍的提速。

图12 论文[13]中基于GPU的布局优化的软件框架和流程图

图片来源:https://ieeexplore.ieee.org/document/8807076

结论与思考

上述的文章主要介绍了近些年来ML在EDA研究中的成果,主要围绕在EDA中某一个环节进行针对性的研究,由于可扩展性存在问题,距离工业应用还有一定的距离,但学术界的研究让人们看到了ML在EDA应用的潜力。

虽然基于图像的NN可以应用到EDA中,但是必须仔细构建模型才能解决诸如多组合问题的挑战,但与此同时会遇到扩展性问题,将训练模型应用到比训练模型所解决的问题更广的范围时,性能将会大大折扣。

与此同时,ML解决问题的方式是依赖先验数据,而EDA中获得实际场景的数据很难,因为涉及到IP授权及大量实际芯片设计数据等,针对这些问题需要众多EDA厂商和芯片设计公司的合作,共同推动建立公开的数据集,共同助推行业技术的发展。

最后,EDA经历了近50年的发展,技术发展陷入停滞,而ML方法的引入给EDA带来了一些曙光,也期待着学术研究成果能够推动工业界EDA工具的发展。

参考文献

[1] A. B. Kahng, “Advancing Placement”, Proc. ISPD, 2021, pp. 15-22.

[2] A. B. Kahng, “Machine Learning for CAD/EDA: The Road Ahead”, IEEE Design & Test (2022)

[3] Rapp, Martin, et al. "Mlcad: A survey of research in machine learning for cad keynote paper." IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 41.10 (2021): 3162-3181.

[4] S. Dai, Y. Zhou, H. Zhang, E. Ustun, E. F. Young, and Z. Zhang, “Fast and accurate estimation of quality of results in high-level synthesis with machine learning,” in Proc. IEEE Int. Symp. Field Program. Cust. Comput. Mach. (FCCM), 2018, pp. 129–132.

[5] E. Ustun, C. Deng, D. Pal, Z. Li, and Z. Zhang, “Accurate operation delay prediction for FPGA HLS using graph neural networks,” in Proc. Int. Conf. Comput.-Aided Design, 2020, pp. 1–9.

[6] G. Zhong, A. Prakash, S. Wang, Y. Liang, T. Mitra, and S. Niar, “Design space exploration of FPGA-based accelerators with multilevel parallelism,” in Proc. Design Autom. Test Europe Conf. Exhibit.(DATE), 2017, pp. 1141–1146. [23] E. Zennaro, L. Servadei, K. Devarajegowda,

[7] Y. Zhang, H. Ren, and B. Khailany, “GRANNITE: Graph neural network inference for transferable power estimation,” in Proc. IEEE Design Autom. Conf. (DAC), 2020, pp. 1–6.

[8] G. Pasandi, M. Peterson, M. Herrera, S. Nazarian, and M. Pedram, “Deep-PowerX: A deep learning-based framework for low-power approximate logic synthesis,” in Proc. Int. Symp. Low Power Electron. Design (ISLPED), 2020, pp. 73–78.

[9] Z. Xie et al., “RouteNet: Routability prediction for mixed-size designs using convolutional neural network,” in Proc. IEEE Int. Conf. Comput.-Aided Design (ICCAD), 2018, pp. 1–8.

[10] C. Yu and Z. Zhang, “Painting on placement: Forecasting routing congestion using conditional generative adversarial nets,” in Proc. Design Autom. Conf. (DAC), 2019, p. 219.

[11] M. B. Alawieh, Y. Lin, Z. Zhang, M. Li, Q. Huang, and D. Z. Pan, “GAN-SRAF: Sub-resolution assist feature generation using generative adversarial networks,” IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 40, no. 2, pp. 373–385, Feb. 2021.

[12] A. Hosny, S. Hashemi, M. Shalan, and S. Reda, “DRiLLS: Deep reinforcement learning for logic synthesis,” in Proc. IEEE Asia South Pac. Design Autom. Conf. (ASP-DAC), 2020, pp. 581–586.

[13] Y. Lin et al., “DREAMPlace: Deep learning toolkit-enabled GPU acceleration for modern VLSI placement,” IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 40, no. 4, pp. 748–761, Apr. 2021

近期文章

商务合作:business@birentech.com

商务合作:business@birentech.com 业务电话:021-68773133

业务电话:021-68773133